QSPI Introduction(Sample STM32)

QSPI介面簡介

QSPI是Queued SPI的簡寫,是Motorola公司推出的SPI介面的擴充套件,比SPI應用更加廣泛。在SPI協議的基礎上,Motorola公司對其功能進行了增強,增加了佇列傳輸機制,推出了佇列序列外圍介面協議(即QSPI協議)。這邊針對QSPI是針對SPI FLASH儲存器做解說。

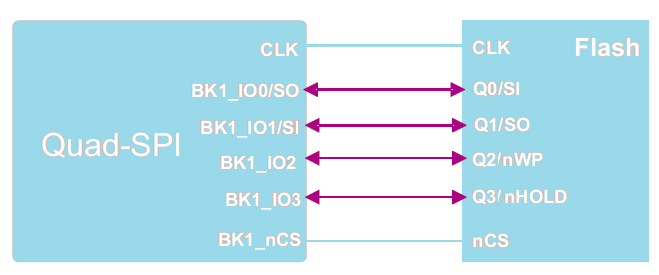

QSPI的使用(Flash)

QSPI 使用 6 個I/O連接Flash,分别是四個數據BK1_IO0~BK1_IO3,一個CLK,選輸出(低電壓有效)BK1_nCS,作用介紹如下:

- BK1_nCS:選輸出(低電壓有效),適用於 FLASH 1。如果 QSPI 始终在雙閃存模式下工作,則其也可用於 FLASH 2從設備選擇信号線。QSPI通訊以BK1_nCS線置低電壓為開始信號,以BK1_nCS線被拉高作為结束信號。

- CLK:時脈輸出,適用個2個存储器,用於通訊數據同步。它由通訊主機產生,决定了通訊的速率,不同的設備支持的最高時脈頻率不一樣,如STM32的QSPI时時脈頻率最大為fpclk/2,2個設備之間通訊時,通訊速率受限於低速設備。

- BK1_IO0:在雙線 / 四線模式中為雙向 IO,單線模式中為串行輸出,適用於FLASH 1。

- BK1_IO1:在雙線 / 四線模式中為雙向 IO,單縣模式中為串行輸入,適用於FLASH 1。

- BK1_IO2:四線模式中為雙向 IO,適用於 FLASH 1。

- BK1_IO3:四線模式中為雙向 IO,適用於 FLASH 1。

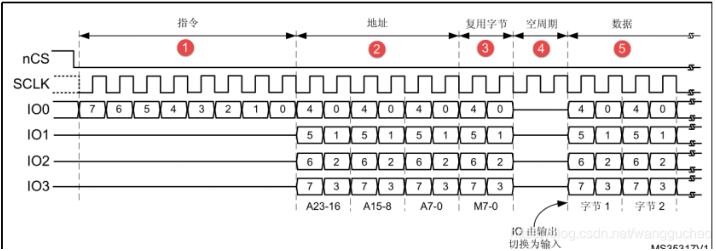

QSPI 命令序列

1. 指令階段

將在 QUADSPI_CCR[7:0] 寄存器的 INSTRUCTION 字段中配置的一條8 bit指令發送到 Flash,指定待執行操作的類型。

儘管大多數 Flash 從 IO0/SO 信號(單線 SPI 模式)只能以一次 1 bit的方式接收指令,但指令階段可選擇一次發送 2 bit(在雙線 SPI 模式中通過 IO0/IO1)或一次發送 4 bit(在四線SPI 模式中通過IO0/IO1/IO2/IO3)。這可通過 QUADSPI_CCR[9:8] 寄存器中的 IMODE[1:0]字段進行配置。

若 IMODE = 00,則跳過指令階段,命令序列從地址階段(如果存在)開始。

2. 地址階段

在地址階段,將1-4字節發送到Flash,指示操作地址。待發送的地址字節數在QUADSPI_CCR[13:12]寄存器的ADSIZE[1:0]字段中進行配置。在間接模式和自動輪尋模式下,待發送的地址字節在QUADSPI_AR寄存器的ADDRESS[31:0]中指定在内存映射模式下,則通過 AHB(來自於 Cortex ® 或 DMA)直接给出地址。地址階段可一次發送1 位(在單線SPI模式中通過SO)、2位(在雙線SPI模式中通過IO0/IO1)或4位(在四線 SPI 模式中通過 IO0/IO1/IO2/IO3)。這可通過QUADSPI_CCR[11:10]寄存器中的ADMODE[1:0]字段進行配置。若 ADMODE = 00,則跳過地址階段,命令序列直接进入下一階段(如果存在)。

2. 交替字節階段

在交替字節階段,將 1-4 字節發送到 Flash,一般用於控制操作模式。待發送的交替字節數在 QUADSPI_CCR[17:16] 寄存器的 ABSIZE[1:0] 字段中进行配置。待發送的字節在QUADSPI_ABR 寄存器中指定。交替字節數段可一次發送 1 位(在單線 SPI 模式中通過 SO)、2 位(在雙線 SPI 模式中通過 IO0/IO1)或 4 位(在四線SPI 模式中通過 IO0/IO1/IO2/IO3)。這可通過QUADSPI_CCR[15:14] 寄存器中的 ABMODE[1:0] 字段進行配置。若 ABMODE = 00,則跳過交替字節階段,命令序列直接進入下一階段(如果存在)。交替字節階段存在僅需發送單個半字節而不是一個全字節的情况,比如採用雙線模式並且僅使用兩個周期發送交替字節時。在這種情况下,固件可採用四線模式 (ABMODE = 11) 並發送一个字節,方法是 ALTERNATE 的位 7 和 3 置“1”(IO3 保持高電位)且位 6 和 2 置“0”(IO2 線保持低電位)。此時,半字節的高 2 位存放在 ALTERNATE 的位 4:3,低 2位存放在位 1 和 0 中。例如,如果半字節 2 (0010) 通过 IO0/IO1 發送,則 ALTERNATE 應設置為 0x8A (1000_1010)。

3. 空指令周期階段

在空指令周期階段,给定的 1-31 个周期内不發送或接收任何數據,目的是當採用更高的CLK頻率時,给 Flash 留出準備數據階段的時間。這一階段中给定的周期數在QUADSPI_CCR[22:18] 寄存器的 DCYC[4:0] 字段中指定。在 SDR 和 DDR 模式下,持續時間被指定为一定個數的全時鐘周期。若 DCYC 為零,則跳過空指令周期階段,命令序列直接進入數據階段(如果存在)。空指令周期階段的操作模式由 DMODE 確定。為確保數據信號從輸出模式轉變為輸入模式有足夠的“周轉”時間,使用雙線和四線模式從Flash 接收數據時,至少需要指定一个空指令周期。

4. 數據階段

在數據階段,可從Flash 接收或向其發送任意數量的字節。在間接模式和自動輪詢模式下,待發送/接收的字節數在 QUADSPI_DLR 寄存器中指定。在間接寫入模式下,發送到 Flash 的數據必須寫入 QUADSPI_DR 寄存器。在間皆讀取模式下,通過讀取 QUADSPI_DR 寄存器獲得從 Flash 接收的數據。在内存映射模式下,讀取的數據通過 AHB 直接發送回 Cortex 或 DMA。數據階段可一次發送/接收 1 位(在單線 SPI 模式中通過 SO)、2 位(在雙線 SPI 模式中通過 IO0/IO1)或 4 位(在四線 SPI 模式中通過 IO0/IO1/IO2/IO3)。這可通過QUADSPI_CCR[15:14] 寄存器中的 ABMODE[1:0] 字段進行配置。若 DMODE = 00,則跳過數據階段,命令序列在拉高 nCS 時立即完成。這一配置僅可用於間接寫入模式。

QUADSPI in a smart architecture

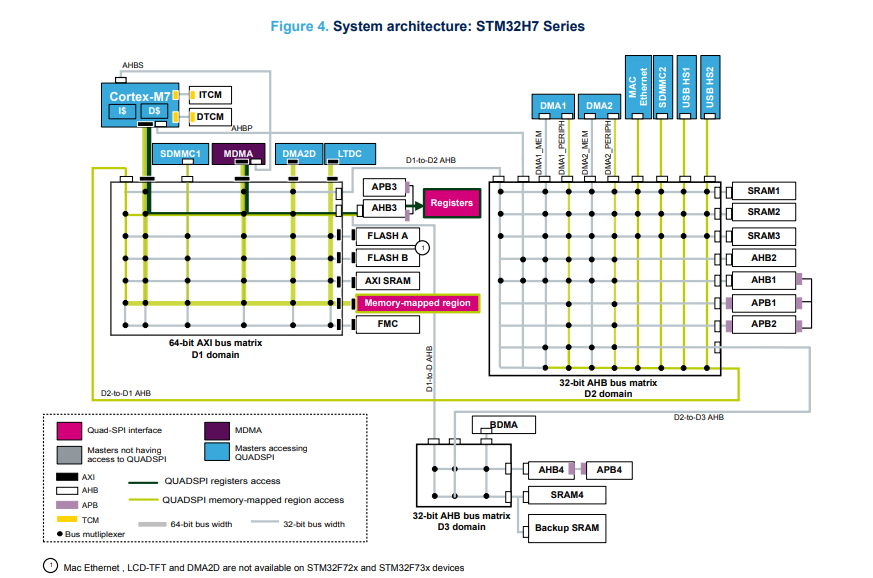

在使用QSPI時須先參考Application note-AN4760這份文件P6確認Domains避免使用上問題已H7較複雜來看有3個Domains

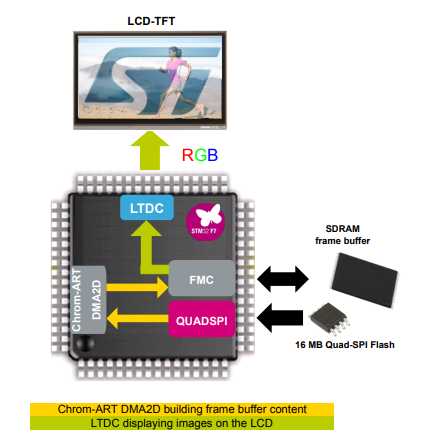

使用QSPI連接LCD結構如如,會使用外部Flash去擴充